Available online at www.jnasci.org ©2013 JNAS Journal-2013-2-11/610-614 ISSN 2322-5149 ©2013 JNAS

# Comparison of bulk driven and sub threshold methods in designing of a typical amplifier

Abdullah Ahmadi<sup>1</sup>, Sina Mohammadi<sup>2</sup>, Hassan Zare<sup>1</sup>and Abdolreza Esmaeli<sup>3\*</sup>

- 1- Department of Electronic, Technical and Vocational College,. Mahmoud Abad, Technical and Vocational University, Iran

- 2- Department of Electrical Engineering, University of Science and Technology, Mazandaran-Babol, Iran

3- Plasma Physics and Nuclear Fusion Research School, Nuclear Science and Technology Research

Institute, Tehran, Iran

# Corresponding author: Abdolreza Esmaeli

**ABSTRACT:** Nowadays one of the most important parameters in designing analog circuits or even in the digital circuits is Reducing the consumption power of the circuit. In analog circuits, power consumption has a direct relationship with the values of circuit supply voltage and given the equation in digital circuits the power can be directly related to the square of the supply voltage value. It is therefore concluded that the reduction of power consumption of analog or digital circuits can be achieved by reducing the supply voltage. Another advantage of low supply voltage is that circuits are easy to transport because the small battery is used as the supply voltage on them. (e.g., audio devices).

*Keywords*: electronic amplifier, bulk driven, sub threshold, power consumption, low voltage supply, CMOS, HSPICE.

# INTRODUCTION

In the industry it is tried to reduce the electronic tools size for easier access to them such as audio devices including mobile. One of the ways to reduce the volume is using the low supply voltage. Because in doing so In addition to reducing the volume of the produced part, its power consumption will also be reduced. Although a reduced supply voltage is suitable to achieve this goal but there are limits to the threshold voltage of transistors and so that the supply value cannot be reduced. However, several methods have been proposed through which one can achieve to a voltage gain and appropriate margin with minimal supply voltage, among them there are sub-threshold, bulk-driven that each has strengths and pitfalls. in the paper it is tried to compare 2 methods in order to deal with their strengths and pitfalls therefore a double floor circuit has been proposed which all mentioned methods have been used in order to design it to reach a 35 dB gain with 6 V supply .then in the next sections we have tried to compare the results considering briefly each method the intended circuit will be designed finally.

## A Brief Study on the sub-threshold method

When the gate - source voltage of a MOSFET transistor is less than the threshold voltage, the Channel is in weak inversion which the area of the performance is called sub-threshold transistor. Device consumption current in the region is an exponential equation:

$$I_{DS} = \frac{2K''w}{l} \left(\frac{nK_T}{q_e}\right) \exp\left[\frac{q(v_{GS} - v_{In})}{nk_T}\right]$$

(1)

$$g_m = \frac{I_D}{nK_T / q}$$

(2)

$$r_0 \cong \frac{1}{\lambda I}$$

(3)

In this region because the amount of transistors current is very low, circuit consumption power will below and also voltage drop on the drain - source terminal is low. Because of these two above important properties in designing the low voltage and power circuits this structure is used. Nearly Similar to a transistor BJT, MOSFET transistor trans-induction is directly related to the transistor current in the sub-threshold area. (J.Rosenfeld, M.Kozak 2004) Because in the sub-threshold area there is low transistor current so the trans-induction value is equal to , it is clear that the channel length plays an important role in the operation thus due to channel length increase the gain value will rise. But its weakness is that due to very low transistor current the trans-induction value of transistor is very small , as a result the gain width and extent of circuit is reduced Because - for example - in a two-floor circuit , the value of circuit single gain width is directly related to the value of input floor trans-induction given the equation (14). Therefore, this type of circuit is used in the low frequency.

$$GBW = \frac{g_m}{c_c}$$

(4)

In this method we make use of the auxiliary and folded cascade circuit with it to strengthen further gain. This structure has pitfalls including:

- 1- It has no a good frequency response.

- 2- For The values  $V_{DS} \prec 3kT/q$ , the equations  $g_m \& r_0$  are non-linear and makes it difficult to design.

- 3- To increase the gain of a transistor the devices width should be high and so the speed of the circuit will be reduced.

## Investigation of body-driven circuits

#### Dependency of the threshold voltage to the body voltage

Usually the body terminal voltage in some cases is named as source of error. But the reality is that although the body terminal and the voltage on which and even the voltage deference between this terminal and especially the source terminal create some problems in designing and probably calculation and we should care about it as a second gate for this and even apply input signal to it and expect the signal amplification by the device in these conditions. Given that different discussions set forth for the arrangements with gate input (gate-driven) such as voltage amplification value , frequency response quality , input & output voltage limit, etc. It is necessary to adopt that whether the body can be as input, the above discussion should investigated. The chapter aims to learn more about transistor circuits with signal input to the body terminal (Bulk - Driven), and exploring some important features of amplifier.

with respect to the threshold voltage relations in the devices PMOS, NMOS:

$$V_{TH} = V_{th0} + \gamma (\sqrt{2\phi f} + V_{SB} - \sqrt{2\phi f}) \text{ NMOS}$$

(5)

$$V_{TH} = V_{th0} - \gamma (\sqrt{2\phi f} - V_{SB} - \sqrt{2\phi f}) \text{ PMOS}$$

(6)

$$I_D = \mu_n C_{ox} \frac{w}{2l} (V_{GS} - V_{th})^2$$

(7)

It can be seen that the rate of voltage changes of body-sou

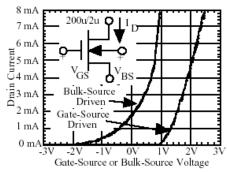

It can be seen that the rate of voltage changes of body-source may impact on the threshold voltage. For example, as shown in Figure 1 due to increase of the body terminal voltage in relation to the source, threshold voltage is reduced. Thus, given the drain current relationship with threshold voltage reduction the drain current increases. Another point is presumable from equations (15),(16) and (17) is that the rate of changes of transistors current is less than that of body-source voltage in comparison to that of source-gate voltage, So when the devices are being used up by the body-driven method they have more input changes than gate –driven state. The quality of the above mentioned matter is shown in Figure 1.

According to Figure 1 in a transistor, n-type increases due to increase in the body voltage relative to the transistor current source.

But what is important is that the body terminal voltage value should also be limited because pad lock or leakage current through device internal diodes will effect on the transistor function.

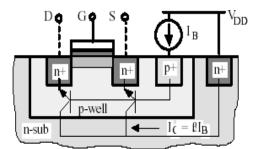

if the input voltage of the body (in the device NMOS) increases, internal bonds PN between the body and source and that of the drain and body source will become active and even activates the links (Figure 2). In addition unwanted BJT transistors may be activated and pad locking happen.

Figure 1. the drain current with respect to body-source and gate - source voltage

Figure 2. internal structure of an NMOS

In DC analysis of transistor circuit, the drain current can be calculated via following equation regardless of any arrangement.

$$ID = \mu_0 C_{ox} \frac{W}{2l} \Big[ V_{GS} - V_{TH0} - \gamma \Big( \sqrt{2\varphi f + V_{SB}} - \sqrt{2\varphi f} \Big) \Big]^2$$

(8)

Which the following equations are defined in:

Saturation region

$$V_{DS} \succ V_{GS} - V_{TH}$$

(9)Triode region $V_{DS} \prec V_{GS} - V_{TH}$ (10)Cut-off region $V_{GS} \prec V_{TH}$ (11)

So the DC voltage of body - source terminal has a feature either in circuits(Bulk-Driven) or in circuits (Gate-Driven) and will change the operating point to the same extent .In Small-signal analysis of a device as body-driven or with gate input or observing small signal model of the amplifiers we will have the following equations . Latch up:

$$g_{mbs} = g_m \times \frac{\gamma}{2\sqrt{2\phi f + V_{SB}}} = \eta g_m \tag{12}$$

$$g_{mbs} = -\frac{\delta ID}{\delta V_s B} = -(\frac{\delta_{iD}}{\delta V_{Th}})(\frac{\delta V_{TH}}{\delta V_s B})$$

(13)

$$g_m = -\frac{\delta ID}{\delta V_{GS}} = -(\frac{\delta_{iD}}{\delta V_{Th}})$$

(14)

$$\frac{\delta_{V_{TH}}}{\delta_{VSB}} = \frac{\gamma}{2\sqrt{2\phi f + V_{SB}}}$$

$$0.2 \prec x \prec 0.4$$

(15)

$$V_{BS} \ge 2\varphi f - 0.25\gamma^2 \cong 0.5V \tag{16}$$

In The small-signal analysis, the drain current in addition to dependency on the gate - source small signal voltage ( $V_{gs}$ ) is depended as well to the Body - source small-signal voltage that the dependency value  $g_m$  and  $g_{mbs}$  is defined via trans-inductions & which in the equations described if  $V_{BS} \ge 2 \# -0.25 \gamma^2 \cong 0.5V$ ,  $g_{mbs}$  is more than  $g_m$ , but the pitfall of this is the high leakage current and probably the pad locking (Ramirez, 1996; Sing, 2003) Relations .As it has been shown in the above equations  $g_{mbs} = \eta g_m$ , this means that the trans-induction value  $g_m$  could even

be five times larger than that of trans-induction  $g_{mbs}$  .i.e. The value of the signal strength by inserting the input into the body is 5 times lower than signal insertion into the gate, and then it is also the weakness of body-driven circuit

Another weakness with the body input is its speed reduction relative to the moment the same device works with input gate frame (Phillip and Benjamin, 2003; Pease, 2000).

$$f_{i\,bulk-driven} = \frac{\eta}{3.8} f_{i\,gate-driven} \tag{17}$$

#### Comparison of methods

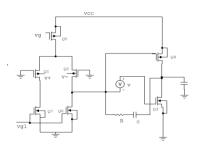

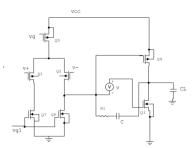

Figures 3, 4 and 5 are respectively the circuits with quite similar structure which their differences are: how to insert the input voltage to the circuit, how to bias and also kind of input transistor. The circuit K in the first floor is a PMOS differential double floor circuit that was used.

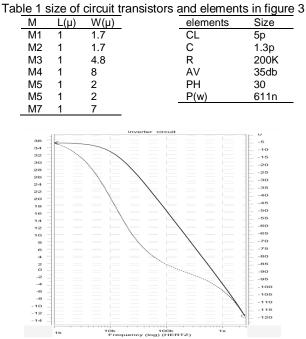

The second floor circuit is a low voltage amplification AB. a voltage source was used to bias the second floor circuit. We examine 3 parameters such as size ,phase margin and consumption power to compare the methods for achieving the voltage gain in 35 dB. Figure 3 shows the circuit with differential pair input in the body-driven layout.

Figure 3. the circuit with body-driven input

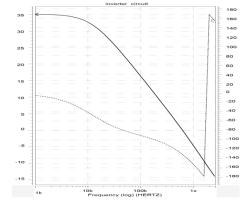

Figure 4. Frequency response of the circuit in Figure 3

Figure 5. the proposed circuit which all devices are biased in sub-threshold region

Table 2 the transistors and elements size of the circuit in Figure 5

| М  | L(u) | W(u) | elements | Size |

|----|------|------|----------|------|

| M1 | 10   | 170  | CL       | 5p   |

| M2 | 10   | 170  | R        | 0.1k |

| MЗ | 2    | 70   | С        | 10n  |

| M4 | 2    | 60   | AV       | 35db |

| M5 | 2    | 40   | PH       | 75   |

| M6 | 2    | 40   | P(w)     | 946n |

| M7 | 2    | 5    | elements | Size |

Figure 6. Frequency response of the circuit in Figure 5

It can be seen that in Comparison of phase margin and In comparison of power consumption two methods are perceived. The sub-threshold method has less consumption power in proportion other methods.

## CONCULSION

In the paper after designing a double floor circuit by 2 methods which has been carried out through 0/6 V supply voltage; it was evident that even if all of them can be used in low supply voltage very well but depending on the overall goal everyone can be used. For example, if circuit design target is led to very low consumption power the sub-threshold technique is the most appropriate one However; its low frequency response still remains as before or if the objective of circuit design is with a suitable volume of bulk.

#### REFERENCES

- Rosenfeld J, Kozak M. 2004. "A Bulk-Driven CMOS OTA with 68db DC Gain," 11 th IEEE International conference.on circuit and System,ICECS 2004,dec.2004,pp.5-8.

- Ramirez J. 1996. "Low Supply Voltage Ota Artitecture Using Floating Gate Transistors"IEEE Electrical and computer engineering.

Sing B. 2003. King Fahd university of petroleum and Minerals "Ultera-LowVoltage Operational amplifier".

- Philllip E and Allen Benjamin J. 2003. Blalock scool of electrical and computer engineering Georgia institute of technology Atlanta"Low voltage analog circuits using standards Cmos technology".

- Pease R. 2000. "The Design Of Band- gap circuits" IEEE 1990 Bipolar and circuitTechnology Meeting, PP 214-218.